En el mundo del diseño de circuitos de alta frecuencia, mantener la integridad de la transmisión de señales es primordial. Si la impedancia característica de la línea de transmisión no coincide con la impedancia de los componentes o conectores, puede provocar reflexión o pérdida de señal, lo que a su vez degrada el rendimiento general del sistema. Incluso con un ajuste cuidadoso de la impedancia de la línea de transmisión, pueden ocurrir cambios inesperados de impedancia en el punto de conexión de los componentes.

Este artículo explica medidas y métodos de simulación para evitar tales problemas. Específicamente, se centra en el impacto de los patrones de huellas de los componentes en la impedancia e introduce técnicas de diseño y simulación apropiadas para mantener la calidad de la señal.

El papel de la impedancia característica

La impedancia característica en la línea de transmisión, que indica la relación entre el voltaje y la corriente, es esencial para la transmisión precisa de la señal.

Sin embargo, la forma del patrón de huella del componente puede causar una degradación inesperada de la señal. Normalmente, los patrones de huella se diseñan más grandes para facilitar la soldadura y asegurar que los componentes estén fijados de manera segura, pero este diseño puede introducir una capacitancia parásita no deseada, afectando negativamente la impedancia.

En el diseño de circuitos de alta frecuencia, incluso estos efectos menores pueden llevar a problemas significativos, por lo que es crucial comprender estos impactos a través de la simulación y el análisis.

Simulación del patrón de huella del conector U.FL

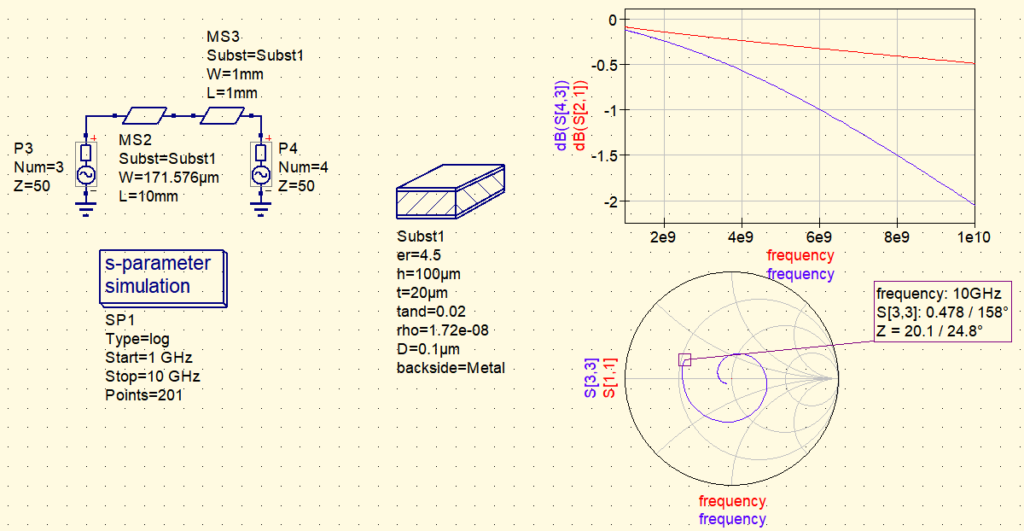

Simularemos un ejemplo de diseño utilizando el patrón de huella recomendado del conector U.FL, un conector coaxial ampliamente utilizado, en una línea microstrip de 50Ω con Qucs Studio.

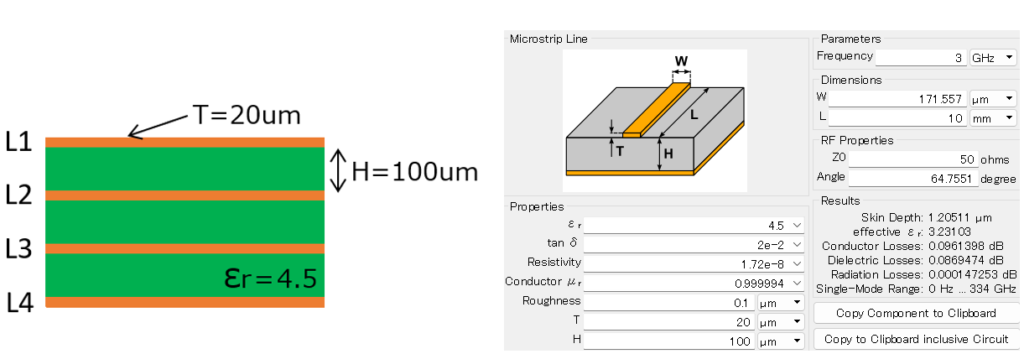

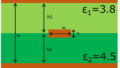

Esta vez, diseñamos una línea microstrip de 50Ω utilizando las capas L1 y L2 del PCB especificado. Al diseñar con el «Calculador de Líneas de Transmisión», el ancho de la pista para 50Ω es de 171μm.

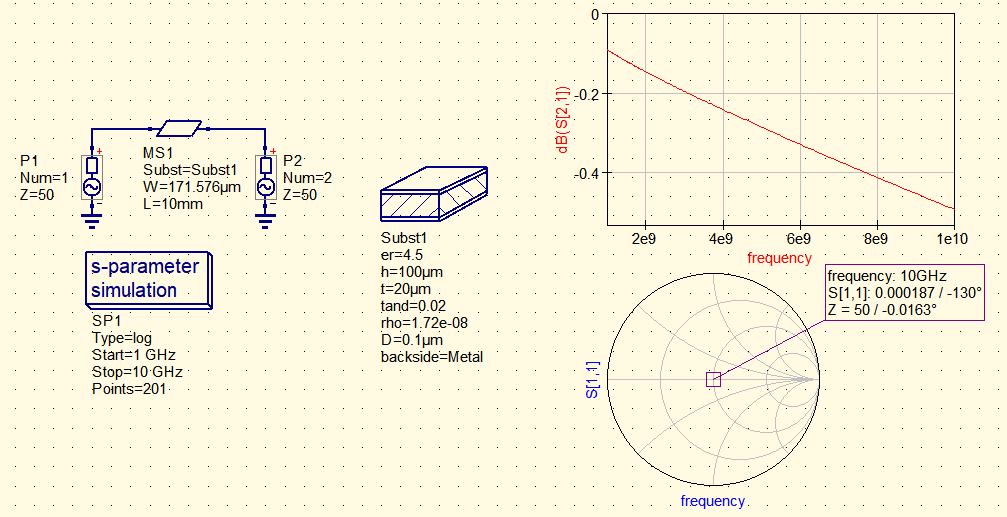

Al simular esta línea microstrip, podemos confirmar que la impedancia característica es de 50Ω, y las características de transmisión son buenas.

A continuación, realizamos la simulación de conectar el conector U.FL a la línea microstrip y observamos el impacto del patrón de huella.

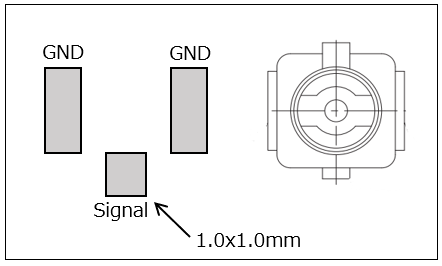

El patrón de huella recomendado para U.FL sugiere que el pin de señal forme una tierra con un cuadrado de 1.0×1.0mm, considerando el aspecto de implementación.

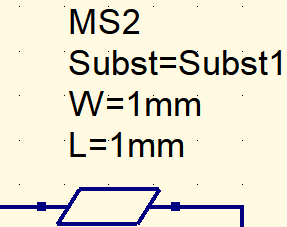

El modelo de simulación para esta tierra se crea de manera similar a la línea microstrip usando el «Calculador de Líneas de Transmisión». La constante dieléctrica y la altura (H) del sustrato permanecen iguales, especificando W=1.0mm y L=1.0mm.

Los resultados de la simulación demuestran que el patrón de huella recomendado para los componentes puede afectar la impedancia característica y potencialmente degradar las características de transmisión del circuito.

Rojo: solo línea microstrip Azul: línea microstrip + patrón de huella

Causas de la reducción de la impedancia

Al colocar el conector U.FL, el aumento en el tamaño del patrón de huella conduce a un incremento en la capacitancia parásita, que es un factor principal que afecta la impedancia característica.

La impedancia característica se calcula en base a los valores de inductancia y capacitancia, y a medida que aumenta el tamaño del patrón de huella, también lo hace la capacitancia, lo cual, a su vez, reduce la impedancia.

Soluciones para reducir la caída de impedancia

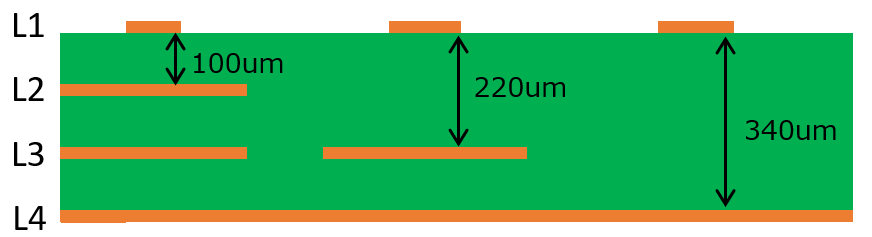

Para mitigar la reducción de la impedancia, la optimización del patrón de huella es efectiva. La capacitancia parásita se determina por el tamaño del patrón de huella y la distancia hasta la capa GND.

Aumentar la distancia a la capa GND puede reducir la capacitancia parásita.

Por lo tanto, eliminar las capas debajo del patrón de huella puede mejorar esta situación.

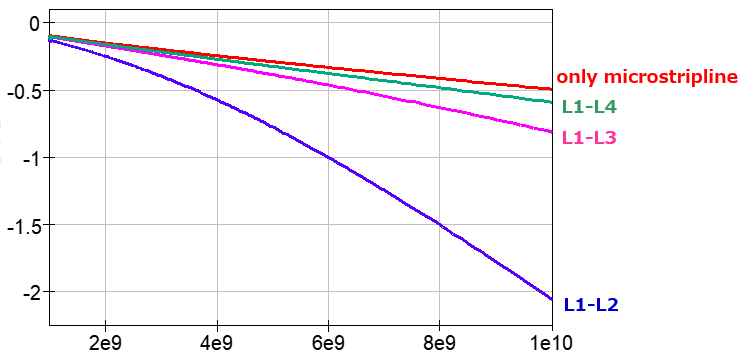

Al eliminar las capas L2 o L3 y colocar el patrón de huella, puede aumentar el espacio libre hasta GND, reduciendo así la capacitancia parásita.

Simular las características de paso del patrón de huella con un espacio libre aumentado muestra que expandir la distancia a GND y reducir la capacitancia parásita puede mitigar el impacto de la reducción de la impedancia.

Conclusión

Este artículo abordó la importancia de la integridad en la transmisión de señales en el diseño de circuitos de alta frecuencia y los problemas que causa la falta de coincidencia en la impedancia. Examinamos específicamente el impacto de los patrones de huellas de los componentes en la impedancia, utilizando el conector U.FL como ejemplo, y revelamos sus efectos mediante la simulación.

También tocamos la importancia de la optimización del patrón de huellas como solución para la reducción de la impedancia. Con esta información, se pueden lograr diseños de circuitos de alta frecuencia más efectivos.

コメント