No mundo do design de circuitos de alta frequência, manter a integridade da transmissão de sinais é de extrema importância. Se a impedância característica das linhas de transmissão não corresponder à dos componentes ou conectores, podem ocorrer reflexões ou perdas de sinal, o que pode diminuir o desempenho geral do sistema. Mesmo ajustando cuidadosamente a impedância da linha de transmissão, podem ocorrer mudanças inesperadas de impedância nos pontos de conexão dos componentes.

Neste artigo, explicaremos as medidas e métodos de simulação para evitar esses problemas. Especificamente, focaremos no impacto das padrões de montagem dos componentes na impedância, e apresentaremos técnicas de design e simulação adequadas para manter a qualidade do sinal.

Papel da Impedância Característica

A impedância característica nas linhas de transmissão indica a relação entre a tensão e a corrente, sendo essencial para garantir a transmissão precisa do sinal. No entanto, o formato dos padrões de montagem dos componentes pode causar degradação do sinal. Normalmente, os padrões são projetados para facilitar a soldagem e garantir uma fixação sólida dos componentes, mas um design muito grande pode gerar capacitância parasita indesejada e afetar negativamente a impedância. No design de circuitos de alta frequência, é crucial simular e analisar esses pequenos efeitos, pois podem causar grandes problemas.

Simulação do Padrão de Montagem de Conectores U.FL

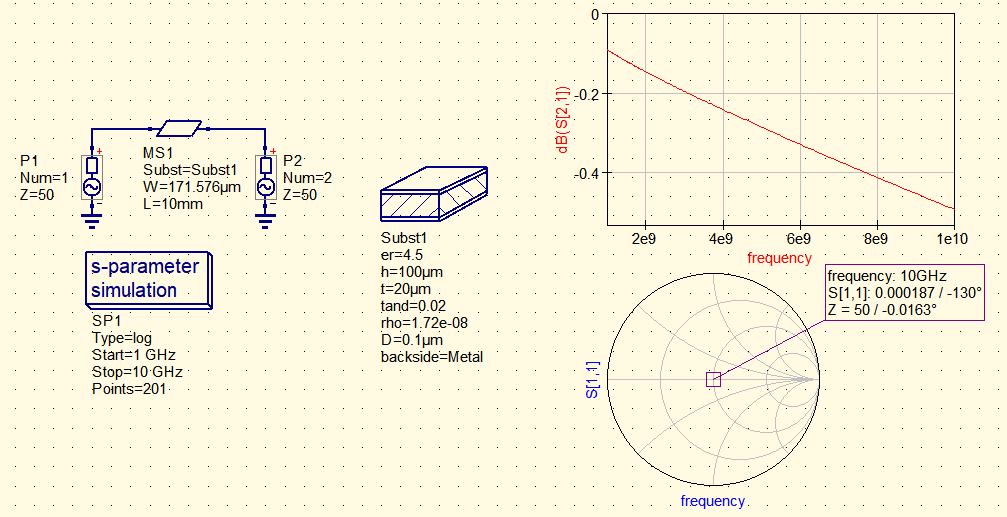

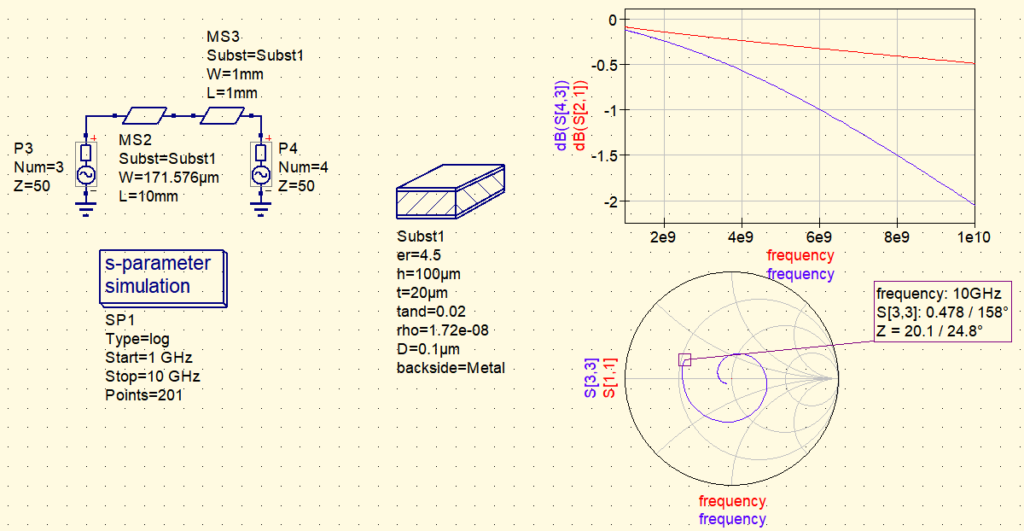

Vamos simular um exemplo de design utilizando conectores coaxiais U.FL amplamente utilizados em linhas de microstrip de 50Ω, usando o software Qucs Studio.

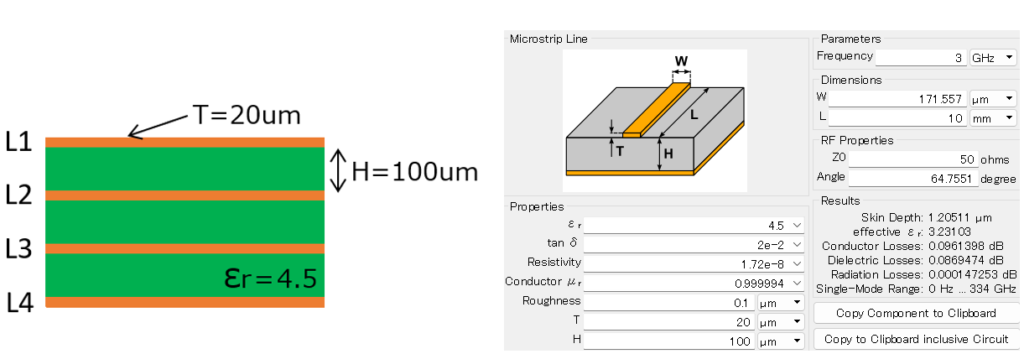

Neste exemplo, usaremos as camadas L1 e L2 de um PCB com as seguintes especificações para projetar uma linha de microstrip de 50Ω. Utilizando o Transmission Line Calculator, a largura da trilha para obter 50Ω é de 171μm.

A simulação desta linha de microstrip mostra uma impedância característica de 50Ω com boas características de transmissão.

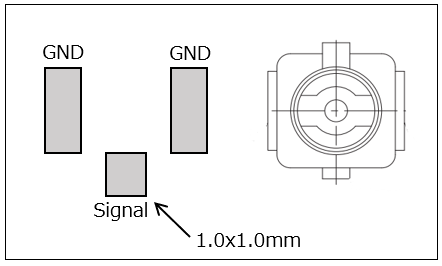

Em seguida, simularemos a adição de um conector U.FL na linha de microstrip e observaremos o impacto do padrão de montagem. A recomendação de design para o padrão de montagem do conector U.FL é formar uma área de contato quadrada de 1.0×1.0mm para o sinal, conforme mostrado abaixo.

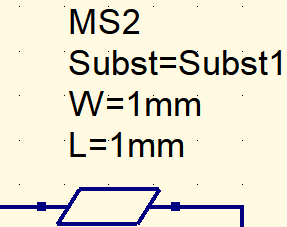

Criamos o modelo de simulação deste padrão usando o Transmission Line Calculator, mantendo a mesma permissividade e altura do substrato da linha de microstrip, mas definindo W=1.0mm e L=1.0mm.

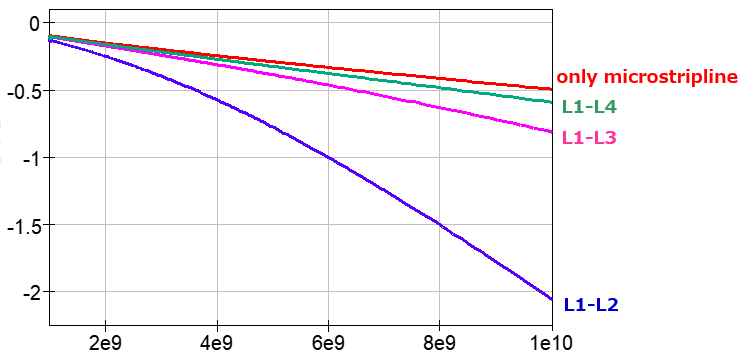

Os resultados da simulação mostram que o padrão de montagem recomendado dos componentes pode afetar a impedância característica e prejudicar as características de transmissão do circuito. Vermelho: apenas linha de microstrip, Azul: linha de microstrip + padrão de montagem

Causas da Redução de Impedância

Na concepção dos conectores U.FL, o tamanho grande do padrão de montagem aumenta a capacitância parasita, o que tem um impacto significativo na impedância característica. A impedância característica é calculada com base na indutância e na capacitância, e um padrão maior aumenta a capacitância, resultando em uma redução de impedância.

Soluções para Reduzir a Diminuição da Impedância

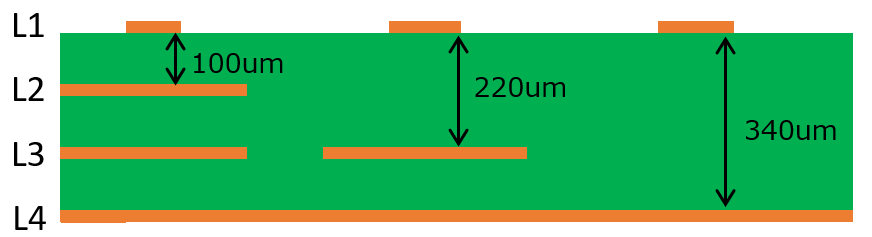

Para minimizar a redução da impedância, é essencial otimizar os padrões de montagem. A capacitância parasita depende do tamanho do padrão de montagem e da distância até a camada de massa. Ao aumentar essa distância, a capacitância parasita pode ser reduzida.

Portanto, remover as camadas inferiores do padrão de montagem pode ajudar a resolver esse problema.

Ao configurar o padrão de montagem de forma a remover as camadas L2 e L3 sob o padrão, é possível aumentar a distância do plano de massa e reduzir a capacitância parasita.

A simulação das características de transmissão deste novo padrão mostra que o aumento da distância do plano de massa reduz o efeito da diminuição da impedância.

Conclusão

Neste artigo, discutimos a importância da integridade da transmissão de sinais no design de circuitos de alta frequência e os problemas causados por uma má correspondência de impedância. Estudamos especialmente o impacto dos padrões de montagem dos componentes na impedância usando o exemplo dos conectores U.FL e demonstramos esses efeitos por meio de simulação. Também apresentamos a otimização dos padrões de montagem como solução para reduzir a diminuição da impedância. Utilizando essas informações, você pode melhorar suas concepções de circuitos de alta frequência de forma mais eficaz.

📌 Ver a ordem de leitura recomendada (Roadmap)

➡️ Próximo (recomendado): Guia de projeto de LPF (componentes ideais)

Comment