串扰是在高速数字电路和高密度布线中不可避免的现象。 在实际设计现场,串扰往往以设计规则的形式被提及, 例如增加走线间距、走线正交、将 GND 布线靠近信号线等, 但为什么这些方法有效,却很少被深入解释。

因此,串扰常常被当作“依靠经验来处理的噪声”。

在讨论具体对策之前,本文将 从电路层面系统整理串扰产生的原因。 关键在于,串扰并不是一种特殊的异常现象, 而是由电路图中未体现的寄生参数所必然导致的结果。

串扰的定义

串扰是指, 某一信号线的时间变化在相邻信号线上感应出不期望的电压或电流的现象。

需要强调的是,信号线之间在直流意义上并未连接, 数据也并不是以“泄漏”的形式传输。 串扰是由于电磁耦合而产生的。 因此,只要 PCB 上存在布线,串扰就不可能完全为零。

表面解释与本质差异

关于串扰,常见的说法包括:

- “因为走线太近,所以会产生串扰”

- “高速信号不可避免会有串扰”

- “这是 EMC 问题”

这些说法作为现象描述并没有错误, 但并未解释设计决策所需的因果关系。 如果无法说明为什么距离变近会恶化串扰, 为什么上升沿时间会产生影响, 以及为什么端接方式和 GND 结构会改变结果, 那么设计规则最终只会变成一份检查清单。

串扰的本质:由寄生参数引起的耦合

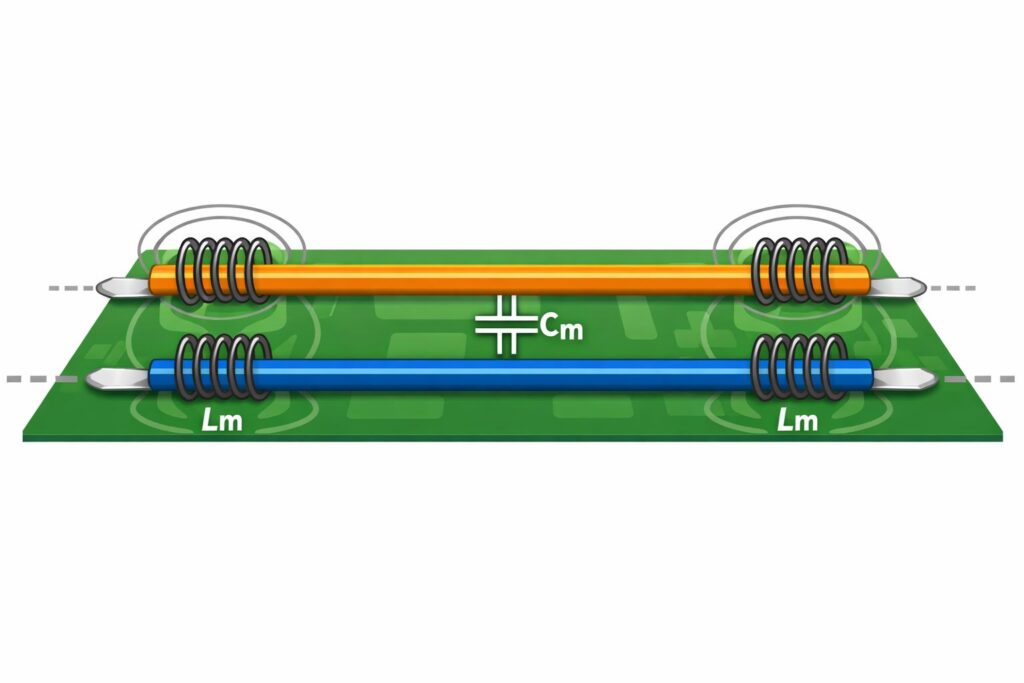

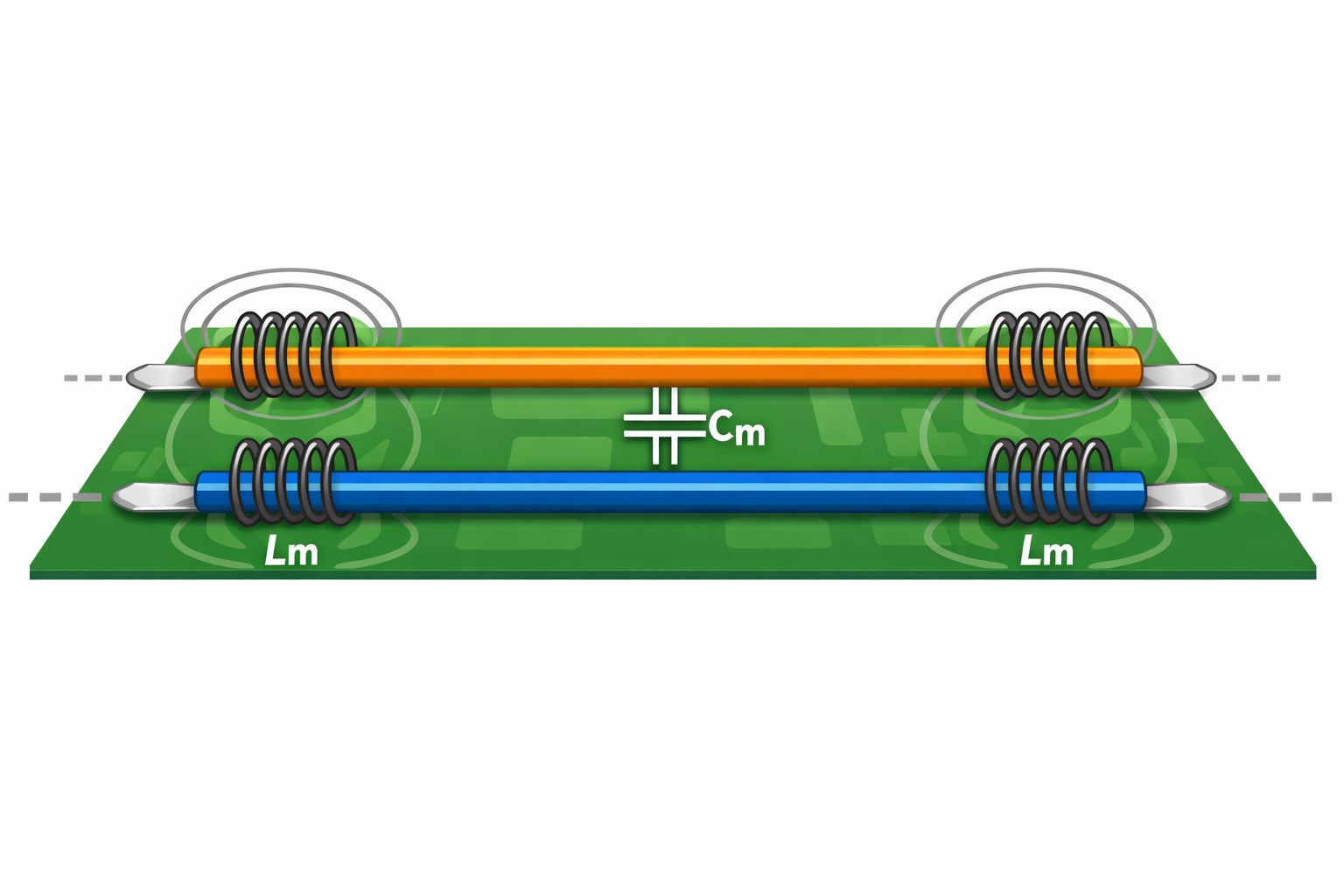

串扰的原因是明确的。 信号线之间会无意中形成寄生参数。 在实际 PCB 上,相邻走线之间会产生 耦合电容(Cm), 而由信号线及其回流路径构成的电流回路之间, 则会形成耦合电感(Lm)。

在电路图中,每一条信号线都被表示为独立的网络。 但在实际硬件中,走线共享同一空间, 并在工作过程中产生电场和磁场。 结果是,电压变化通过电场影响相邻走线, 而电流变化则通过磁场影响其他走线回路。

串扰正是 通过这些未在电路图中体现的寄生参数而发生能量耦合的现象。 下图以示意方式展示了 “在电路图中不存在,但在实际硬件中必然存在的耦合”。

电场耦合与磁场耦合

由寄生参数引起的耦合可以分为两种性质不同的机制。

电场耦合(电容性耦合)

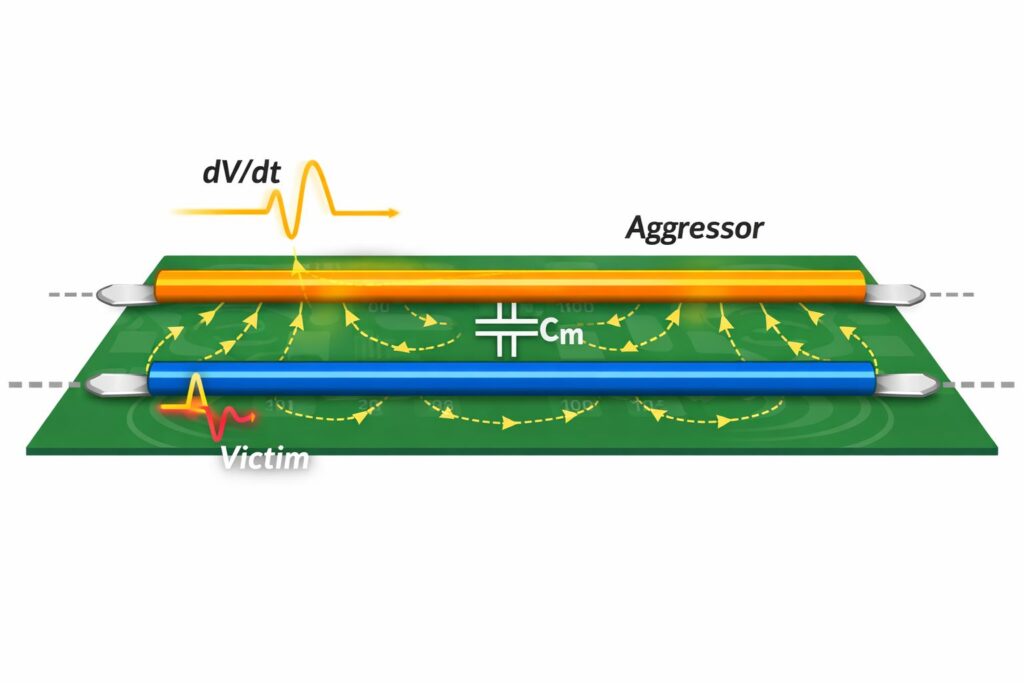

电场耦合通过相邻走线之间形成的 耦合电容 Cm而发生。 当信号线上的电压随时间变化时, 其周围会扩展出电场,并影响邻近走线。

关键在于,耦合强度并不取决于电压的绝对值, 而取决于电压变化率(dV/dt)。 上升沿或下降沿越陡峭, 通过耦合电容在相邻走线上感应出的电压就越大。

下图展示了随着 Aggressor 走线电压变化, 电场扩散并部分耦合到 Victim 走线的过程。 在 Victim 走线上观察到的噪声, 通常与 Aggressor 信号边沿在同一时刻出现。

磁场耦合(电感性耦合)

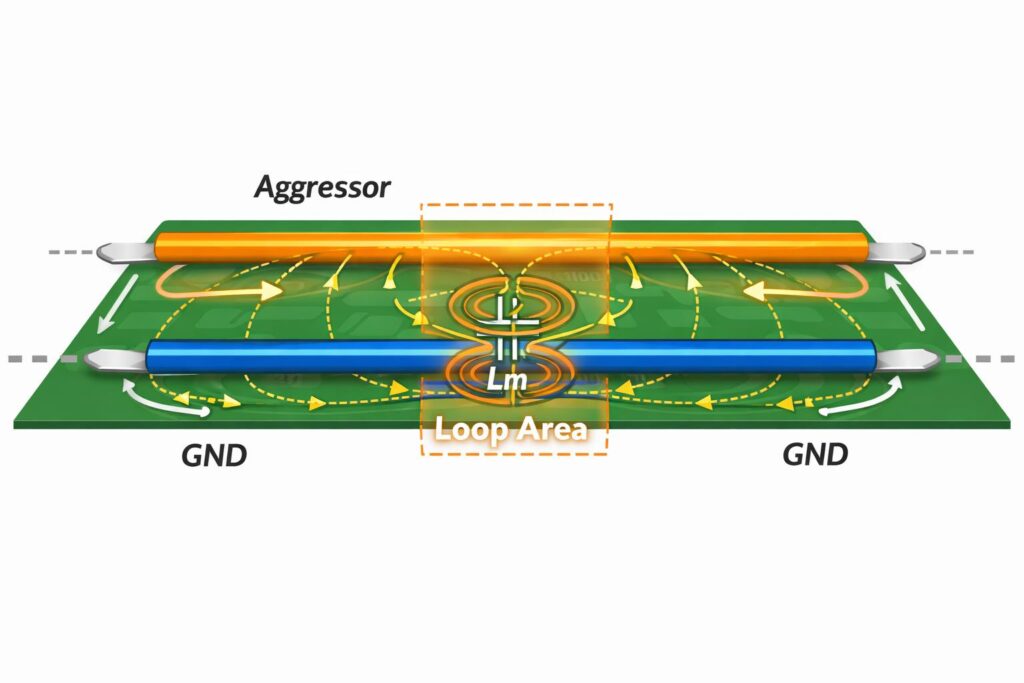

磁场耦合发生于 由信号线与其回流路径(GND)构成的电流回路之间, 这些回路通过磁通量相互耦合。 当电流随时间变化时, 回路周围会产生磁场,从而影响邻近回路。

磁场耦合的主要决定因素是 回路面积。 信号线与 GND 距离越远,回路面积越大, 耦合电感 Lm 也会随之增大。

下图展示了不同 GND 布线方式下, 回路形状的变化以及磁通耦合量的差异。 将 GND 靠近信号线、确保连续的回流路径等设计规则, 本质上是通过 减小回路面积来抑制磁场耦合。

为什么上升沿时间成为主导因素

串扰几乎不依赖于信号的绝对电平。 真正起决定作用的是时间微分分量。

- 电场耦合:电压的时间变化(dV/dt)

- 磁场耦合:电流的时间变化(dI/dt)

因此,即使时钟频率较低, 只要信号边沿足够陡峭,串扰仍然会变得明显。 这也是“高速信号因为高频而产生问题”这一说法不够准确的原因。

uSimmics 可视化的范围

uSimmics(原 QucsStudio)并不是用于精确预测 实际 PCB 串扰量的工具。 但它可以在时间域中分别观察 仅包含耦合电容、 仅包含耦合电感, 以及两者同时存在时的波形差异。

这对于理解串扰由什么引起,以及哪个因素占主导非常有效。 关键不在于数值的精确性, 而在于能够清晰地识别 哪一个寄生参数在什么时刻起作用。

总结

本文并未将串扰视为设计规则的结果, 而是将其整理为电路层面的因果关系。

串扰并不是一种特殊的噪声现象, 而是只要存在布线就不可避免的电磁耦合。

在实际 PCB 上, 耦合电容(Cm)存在于相邻走线之间, 耦合电感(Lm)存在于由信号线及其回流路径构成的电流回路之间。 即使这些寄生参数没有出现在电路图中, 它们也始终存在。

电场耦合主要取决于电压变化率(dV/dt), 磁场耦合则取决于电流变化率(dI/dt)和回路面积。 因此,串扰的大小相比信号频率本身, 更强烈地受上升沿时间和回流路径结构的影响。

增加走线间距、将 GND 靠近信号线、添加端接电阻等设计对策, 并非仅仅是经验法则, 而是降低寄生参数耦合的物理手段。

至此,“噪声对策”的原因 → 波形 → 对策已经完整串联起来。如果想重新确认整体框架,建议从第一篇开始再读一遍。

▶ 返回:噪声对策入门:去耦电容、磁珠、GND铺铜到底是为了什么?

Comment