提到噪声对策,很多人会先想到“先加个去耦电容(旁路电容)”“先加个磁珠”。当然,这些方法在很多情况下确实有效,但如果只靠经验拍脑袋推进,很容易变成“为什么有效说不清”,下次也就难以复现。

本文会介绍一个用于整理噪声对策的基础框架。同时,我们会使用uSimmics(QucsStudio)搭建一个非常简单的电路模型,通过仿真波形来说明:电路图上看不见的要素(寄生参数)会如何影响波形。

把噪声问题分成3类,更容易整理

当你感觉“可能是噪声导致的”时,先把现象(症状)分成3类,会更容易理清思路。

- 误动作:数字信号H/L判定出错、意外复位、通信掉线、误中断

- 性能劣化:接收灵敏度下降、SNR变差、抖动增大、图像/音频失真

- 对外影响 / 规范不合格:超标的辐射/传导发射(EMI),对周边设备产生干扰,EMC测试不过

这3类是按症状来整理的。但从原因结构来看,它们往往是相似的,都可以用发生源 → 传播路径 → 受害点来解释(例如:辐射超标时,“发生源=开关动作”,“路径=走线/外壳”,“受害点=周边设备”)。因此,无论是产品内部问题(误动作/性能劣化)还是对外问题(EMI/EMC合规),都可以用同一套思路分析。

噪声对策的基本框架:发生源 → 传播路径 → 受害点

噪声“存在”并不等于“有问题”。它通常是在产生之后,沿着某种方式传播/耦合,再进入敏感点时,才会变成可见的问题。

- 发生源(Source):开关动作、时钟、DC/DC、电平快速翻转的I/O、马达/继电器等

- 传播路径(Path / Coupling):走线、电源、GND、线缆、空间(电容/电感耦合、反射、共阻抗等)

- 受害点(Victim):射频/接收电路、参考电压、ADC、时钟输入、复位线、传感器线等

用这三个点去看,往往更容易判断:到底应该“先动哪里”才有效。

优先级怎么排?(一个简单顺序)

为了减少返工,一个常用的默认顺序如下:

- 能弱化发生源就最强:放慢边沿、降低驱动能力、改变频率、使用扩频等(可能与性能有取舍)

- 发生源停不掉就控制路径:整理回流路径(return path)、减小回路面积、加终端、滤波、屏蔽等

- 最后让受害点更“耐噪”:即便噪声进入也不误判——增加裕量、稳定输入(迟滞/RC)、必要时加保护器件并优化布线,让它“更不容易进来 / 更不容易被损坏”

在实际硬件中,“控制传播路径”往往最常见也最有效。特别是在PCB上,电路图没画出来的寄生参数常常决定了路径长什么样。

电路图看不见的“犯人”:寄生参数(L/C/R)

很多噪声问题的关键不在原理图上,而在“实际结构”。下面三个要素非常常见。

走线/过孔像电感(L)

走线、过孔以及GND回流路径都带有电感。当电流变化很快(di/dt很大)时,这个电感会产生L × di/dt的电压降。

理想情况下,GND在任何位置都是0V。但真实的GND是由走线/铜箔/过孔连接起来的导体网络,因此这个电压降会让“该位置的GND电位”上下波动。这就是常说的地弹(Ground Bounce)。

当GND在动时,复位脚和参考电压会“相对地”发生变化,于是就可能出现误复位、误判定等问题。

相邻走线像电容耦合(C)

两根相邻走线之间存在微小的耦合电容。也就是说,就算原理图没画,它们也会像两根线之间有一个“小电容”那样工作。

当其中一根线的电压快速变化(dv/dt很大)时,会通过耦合电容产生一个瞬时电流脉冲。这个电流会在另一根线上形成微小的电压变化,在波形上常表现为尖峰(spike)。

这种“某条线的变化进入另一条线”的现象就是串扰(Crosstalk)。边沿越快尖峰越明显,而受害线阻抗越高,波形上越容易看到它。

“损耗(R)”同样重要

理想的L和C只负责储能与回馈,并不会把能量变成热。因此一旦出现振铃(ringing),往往不容易自己停下来。

要让振铃收敛,需要一个“把能量带走”的机制,这就是损耗(R)。R会把能量消耗成热,从而让振荡衰减。

磁珠之所以常常有效,也可以用这个角度解释:磁珠在高频时更容易体现出损耗成分,可以把高频振铃和尖峰“以热的形式消耗掉”。

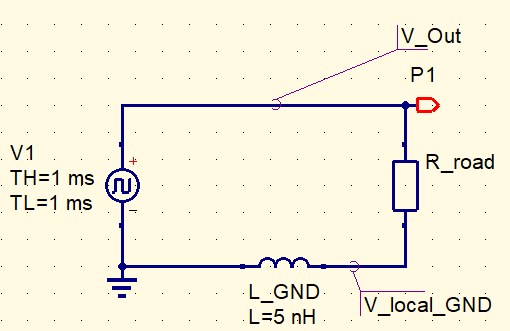

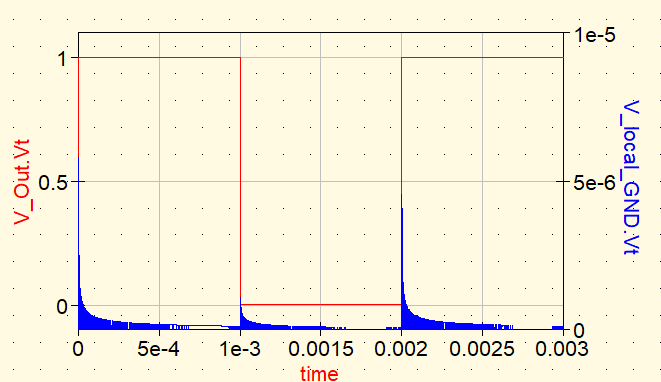

用uSimmics说明:GND并不是理想的0V

这里我们用uSimmics搭一个极小的电路模型,通过波形确认“只要有寄生L,GND就可能会动”。目的在于抓住噪声传播路径(Path)是如何形成的。

电路示意

- VPulse(0 → 1V脉冲)

- Rload(负载电阻)

- GND

- 在GND回流路径中加入一个很小的电感(例如5nH),用来代表配线的寄生电感

VPulse → Rload → node(out) → Lgnd(5nH) → GND

观测点(电压探针)

- V(out):Rload输出侧(我们想看的信号点)

- V(gnd_local):Lgnd上侧(电路侧的GND点)

把VPulse的上升沿变快(例如TR=1ns),你会看到V(gnd_local)上出现一个小脉冲。这就是“回流路径电感导致GND被抬高”的现象。

也就是说,问题不一定只是“信号波形很脏”。有时是基准(GND)在动,从而引发误动作或性能劣化。

整理定番对策的意义(去耦电容 / 磁珠 / 大面积GND)

下面把常见对策“到底是在解决什么问题”用更直观的方式整理一下。

- 增加去耦电容(旁路电容):把电源线上高频噪声在IC附近就旁路掉,避免IC电源电压晃动。关键是尽量贴近IC电源脚放置;如果离得远,走线寄生电感会让高频电流“过不去”,效果会明显变差。

- 增加磁珠:让高频成分更难通过,从而抑制噪声扩散。例如DC/DC的开关噪声回流到其他电源域,或者噪声进入无线/RF部分时,可以把磁珠放在“脏的一侧”和“干净的一侧”的边界。磁珠在不同频段的效果差异很大,建议按目标频段选型。

- 铺大面积GND(实心地平面):为信号电流提供更近的回流路径,让电流不必远绕。回流越近,回路(去+回)越小,辐射和不想要的耦合也会更少。但如果GND被分割、信号跨过缝隙/开槽,回流会绕远路,反而可能变差,所以要注意电流到底从哪里走。

总结

做噪声对策时,先用发生源 → 传播路径 → 受害点来整理,会更不容易迷路。尤其在PCB上,原理图里看不见的寄生参数(L/C/R)经常决定了路径,噪声沿路径进入受害点后才变成“问题”。

用uSimmics做一个最小模型、看一眼波形,很多“为什么有效”会更容易理解。后续文章会继续用同一套框架,依次讲反射与振铃(终端/传输线)、磁珠(损耗为什么有效)、串扰(耦合C/L)、去耦与GND(共阻抗)等内容,用波形把概念讲透。

接下来是「反射」。我们将用最小电路来整理为什么波形会失真(=看起来像“产生了噪声”的真正原因)。

▶ 下一篇:高速信号中发生的“反射”是什么?用最小电路理解

发表回复