在使用uSimmics(原QucsStudio)计算带状线特性阻抗时,有时会出现理论值与实测值不符的情况。原因之一是蚀刻底切(Etching Undercut)导致导体截面形状发生变化。本文详细解析该现象的产生机理及修正计算方法。

本文要点

- PCB制造减成法的原理与蚀刻底切的产生机制

- 梯形截面对带状线特性阻抗的影响

- 考虑蚀刻底切后的修正计算具体方法

- 将修正值输入uSimmics(原QucsStudio)并重新计算的操作步骤

- 缩小理论值与实测值差距的实用方法

1. 带状线基础与特性阻抗

带状线(Stripline)是一种将信号导体埋入PCB内层,上下被接地层夹住的传输线结构。这种结构能有效抑制电磁波辐射,适合高频(RF/微波)信号传输。

特性阻抗由以下物理参数决定:

- 信号线宽度 W

- 基板相对介电常数 εr

- 介质厚度 H

- 导体厚度 T

将这些参数输入uSimmics(原QucsStudio)的传输线计算器(Transmission Line Calculator),即可进行特性阻抗的理论计算。然而,实际制造工艺中存在使理论值偏离的因素。

2. 减成法与蚀刻底切

减成法的原理

PCB图案成型最常用的工艺是减成法(Subtractive Process)。该方法以全面覆铜的基板为起点,通过蚀刻(化学溶解)去除不需要的铜箔,保留所需的电路图案。减成法成本低、量产性好,被广泛应用于普通多层PCB的制造。

蚀刻底切的产生机制

蚀刻液的设计初衷是从上方溶解铜,但实际上侧面也会同时发生溶解。这种侧向溶解现象就是蚀刻底切(Etching Undercut)。

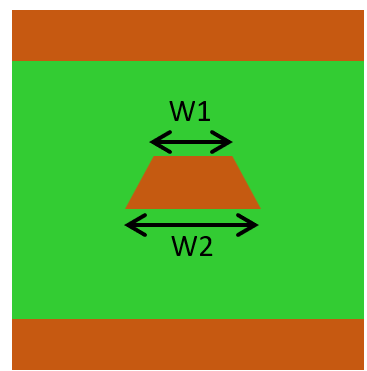

发生蚀刻底切后,设计上应为矩形的导体截面会变为梯形,具体表现如下:

- 光刻胶(掩模)侧的上表面宽度 W2:接近设计值

- 基板侧的下表面宽度 W1:小于设计值(受侧向溶解影响)

这种截面形状的变化会改变信号走线的有效截面积和宽度,直接影响特性阻抗。

3. 梯形截面对特性阻抗的影响

通常的阻抗计算公式以导体截面为均匀宽度的矩形为前提。蚀刻底切使截面变为梯形后,将发生以下变化:

有效走线宽度小于设计值 → 特性阻抗高于设计值

这可以用电容与电感的平衡关系来解释。特性阻抗可表示为:

Z₀ = √(L/C)

其中 L 为单位长度电感,C 为单位长度电容。走线变窄后电容 C 减小,导致 Z₀ 升高。

例如,设计为50Ω的带状线因蚀刻底切而实测为55~60Ω的情况并不罕见。该误差有时会超出阻抗管控的允许范围(通常±10%),对信号质量的影响不可忽视。

4. 蚀刻底切修正计算的操作步骤

步骤1:了解实际尺寸

PCB制造商(供应商)提供的规格书或制造报告中会标注蚀刻底切量。根据该数据了解实际的上表面宽度 W2 与下表面宽度 W1。

根据经验,减成法制造的图案宽度通常比设计值约小10%。例如:

- 设计图案宽度:100 μm

- 实际上表面 W2:100 μm(光刻胶侧,接近设计值)

- 实际下表面 W1:80 μm(基板侧,受蚀刻影响缩小)

步骤2:计算有效宽度(梯形修正)

以梯形截面上、下表面的平均值作为有效宽度:

W_eff = (W1 + W2) / 2

以上例计算:

W_eff = (80 + 100) / 2 = 90 μm

使用修正宽度 W_eff = 90 μm 进行阻抗计算,可显著提高与实测值的吻合度。

步骤3:在uSimmics(原QucsStudio)中重新计算

- 打开uSimmics(原QucsStudio)的传输线计算器(Transmission Line Calculator)

- 在”choice”中选择”Stripline”

- 在”Properties”中输入基板参数

- 在”Dimensions”的”W”(走线宽度)栏输入修正后的有效宽度 W_eff

- 查看计算得出的特性阻抗

通过对比修正前(W = 100 μm)与修正后(W_eff = 90 μm)的特性阻抗,可定量评估蚀刻底切的影响量。

步骤4:反馈至设计值

要实现目标阻抗50Ω,需要在设计图案宽度中预留蚀刻底切余量,将走线设计得更宽。反推步骤如下:

- 在uSimmics(原QucsStudio)的”Z₀”中输入50Ω,计算所需走线宽度 W_ideal

- 考虑蚀刻底切率(例:10%),对设计宽度进行补偿:

W_design = W_ideal / (1 - 底切率)

- 将补偿后的 W_design 反映到制造规格中

5. 进一步提升计算精度的注意事项

| 影响因素 | 对阻抗的影响 | 应对措施 |

|---|---|---|

| 蚀刻底切 | 阻抗升高 | 梯形修正(使用平均宽度) |

| 介电常数制造偏差 | 阻抗分散 | 留有设计裕量 |

| 导体厚度偏差 | 轻微阻抗变动 | 确认制造规格 |

| 温度引起的介电常数变化 | 工作温度范围内的阻抗漂移 | 选用高Tg基材 |

实际的高频电路设计需要综合考虑以上各项因素进行阻抗设计。

6. 总结

uSimmics(原QucsStudio)的带状线阻抗计算功能非常实用,但在实际PCB制造中,蚀刻底切的影响会导致理论值与实测值产生偏差。通过应用梯形修正(使用上、下表面平均宽度),可大幅提升计算精度。建议从制造商处获取实际尺寸规格,并将修正计算纳入PCB设计流程,以实现高品质的阻抗管控。

Comment