在高频电路设计中,维持信号传输的完整性是最重要的。如果传输线的特性阻抗与部件或连接器的阻抗不匹配,就会导致信号反射或损失,进而降低整个系统的性能。即使对传输线的阻抗进行了仔细调整,在连接部件时仍可能发生意外的阻抗变化。

本文解释了避免这些问题的措施和仿真方法。具体来说,关注元件的脚印图案对阻抗的影响,并介绍了维持信号质量的适当设计和仿真技术。

特性阻抗的作用

传输线中的特性阻抗显示了电压和电流的关系,对于信号的准确传输是不可或缺的。

然而,元件的脚印图案的形状可能会导致信号退化。通常,脚印图案被设计得较大以便于焊接和确保元件牢固固定,但这种设计可能引入了意外的寄生电容,从而对阻抗产生负面影响。

在高频电路设计中,这些微小的影响也可能导致重大问题,因此通过仿真和分析详细了解这些影响至关重要。

U.FL连接器脚印图案的仿真

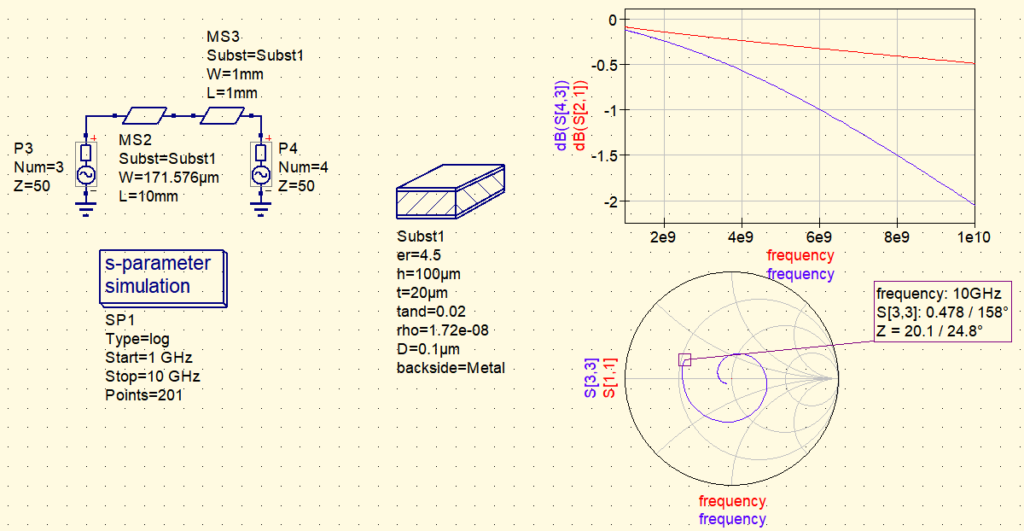

我们将使用Qucs Studio对50Ω微带线上广泛使用的同轴连接器,U.FL连接器的推荐脚印图案进行设计示例仿真。

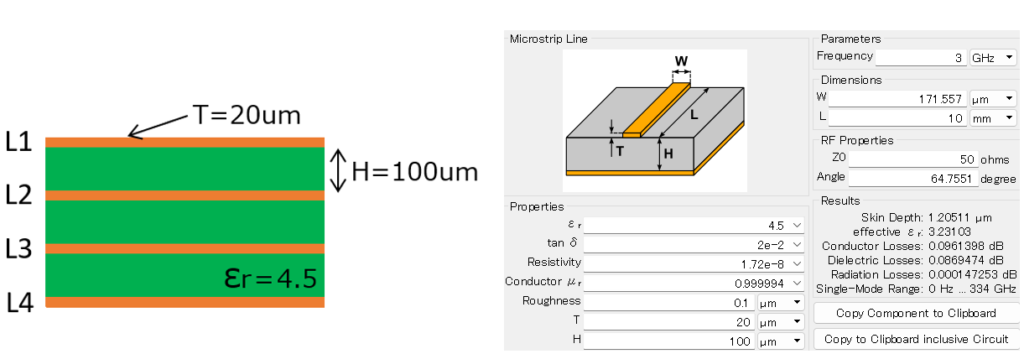

这次我们使用指定PCB的L1和L2层设计了50Ω的微带线。使用“传输线计算器”设计时,50Ω的迹线宽度为171μm。

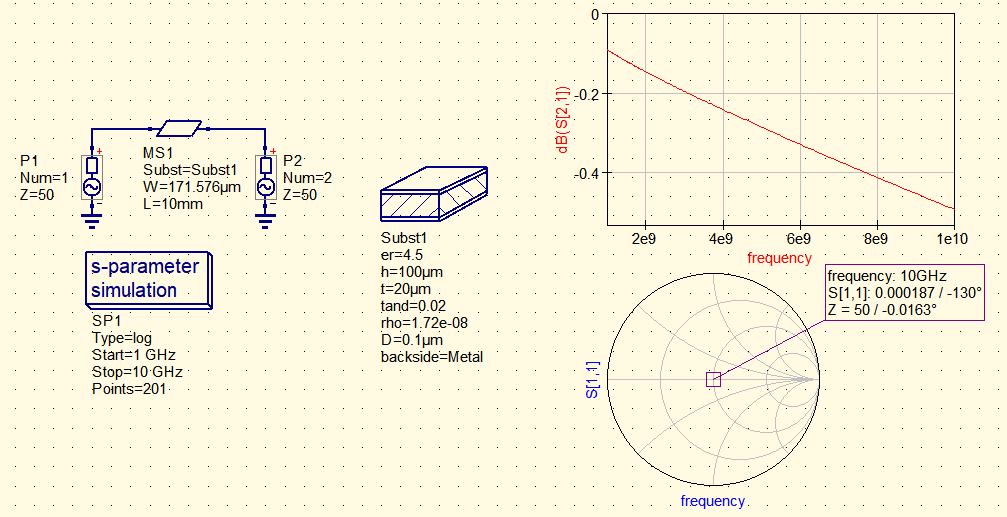

仿真这条微带线时,我们可以确认其特性阻抗为50Ω,传输特性良好。

接下来我们对微带线连接U.FL连接器的情况进行仿真,观察脚印图案的影响。

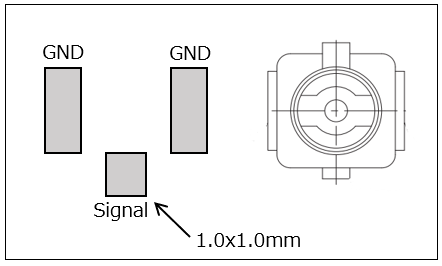

U.FL的推荐脚印图案建议,从实施角度来看,信号引脚应形成1.0×1.0mm的正方形地脚。

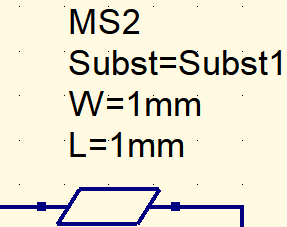

这个地脚的仿真模型与微带线一样,使用“传输线计算器”创建。基板的介电常数和高度(H)保持不变,指定W=1.0mm和L=1.0mm。

仿真结果显示,元件推荐的脚印图案可能会影响特性阻抗,并可能恶化电路的传输特性。

红色:仅微带线 蓝色:微带线+脚印图案

阻抗降低的原因

安装U.FL连接器时,脚印图案的尺寸增加会导致寄生电容增加,这是影响特性阻抗的主要因素。

特性阻抗基于电感和电容的值计算得出,随着脚印图案尺寸的增加,电容也增加,进而导致阻抗下降。

减少阻抗降低的解决方案

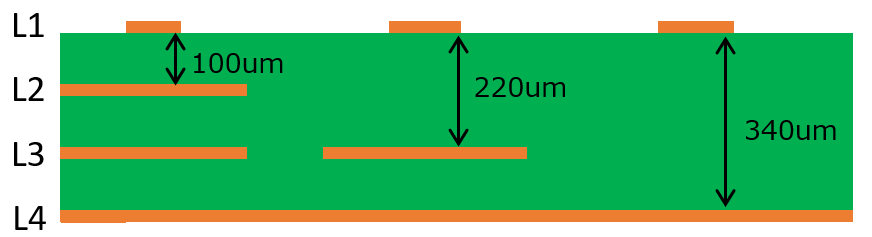

为了减轻阻抗降低,优化脚印图案是有效的。寄生电容由脚印图案的大小和GND层的距离决定。

增加到GND层的距离可以减少寄生电容。

因此,去除脚印图案下的层可以改善这个情况。

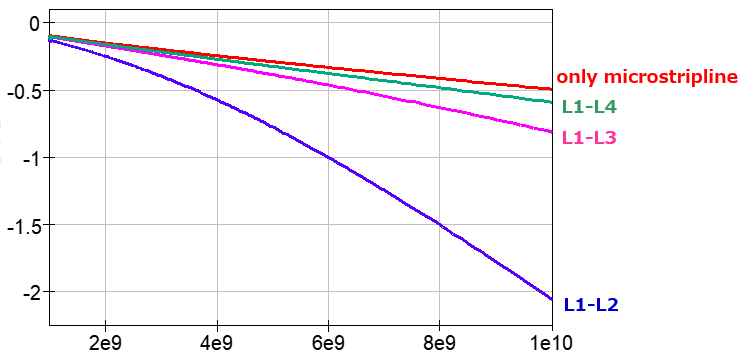

通过去除L2或L3层并放置脚印图案,可以增加到GND的间隙,从而减少寄生电容。

通过这种方式增加间隙的脚印图案的传递特性仿真显示,扩大到GND的距离并减少寄生电容可以减轻阻抗降低的影响。

总结

本文讨论了高频电路设计中信号传输完整性的重要性以及阻抗不匹配引起的问题。我们特别研究了元件足迹模式对阻抗的影响,并以U.FL连接器为例,通过仿真揭示了其效果。

我们还讨论了足迹模式优化作为减少阻抗降低的解决方案的重要性。利用这些信息,可以实现更有效的高频电路设计。

➡️ 下一篇(推荐):低通滤波器(LPF)设计指南(从0到仿真)

发表回复